作者:Iris Yang,AMD工程师;来源:AMD开发者社区

什么是 Tx Preset(发送预设)

Tx Presets 是 PCIe 发送端预定义的均衡设置,包括预加重(pre-emphasis)和去加重(de-emphasis)参数。

该测试的目的是检查被测设备(DUT)在选择不同预设值时的表现情况。

这些预设值会在链路训练阶段(LTSSM 从 Detect 到 L0 状态)被使用,并会对眼图质量和误码率(BER)产生影响。

选择测试环境

你可以通过以下方式进行 Tx Preset(发送预设)测试:

使用官方 PCIe 一致性测试工具(如 Tektronix、Keysight 或 LeCroy)

这些工具通常用于认证测试或高级信号完整性调试。

将被测设备(DUT)连接到 PCI-SIG 认证的测试平台(如 PLTS 或 SigTest)。

按照 PCIe 发送预设一致性测试规范进行测试,基于:

PCI-SIG 基础规范(如 PCIe 4.0 或 5.0)

CEM(卡边缘机械规范)或 PHY 层测试规范

测试步骤:

1.将设备置于一致性测试模式(通过跳线、固件命令或内建自检 BIST)

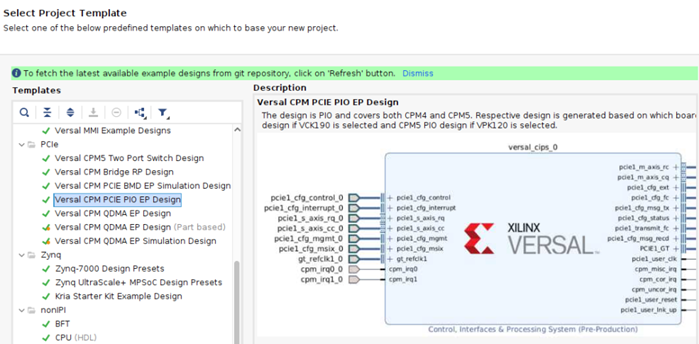

VPK120 需要预先加载一个完整的PCIe 设计,可以直接利用vivado-File-Project -open example 中的设计来测试。比如可以利用下面的设计Versal CPM PCIe PIO 或者其中任意QDMA 设计。

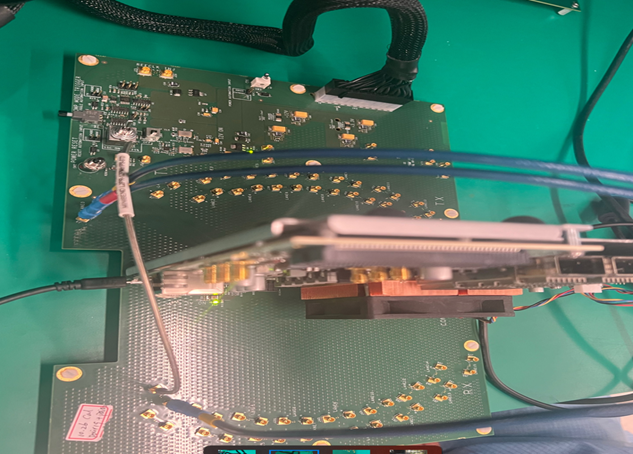

以下为VPK120 插入 CBB5中的连接方式。

2. 选择合适的 Tx 预设值(可通过测试自动化工具或手动控制)

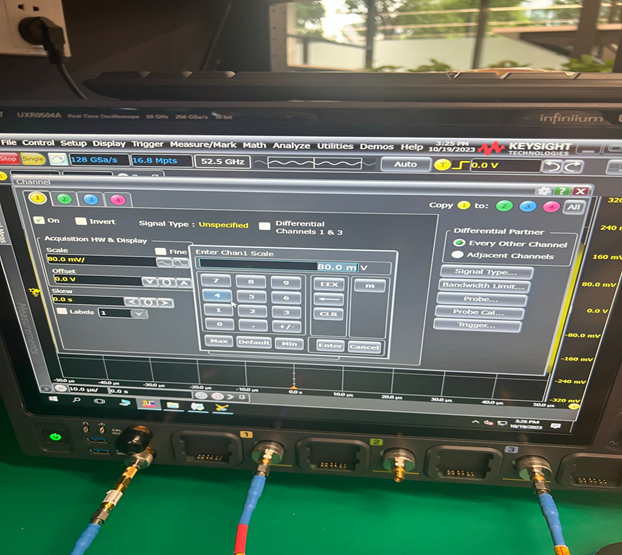

3. 在接收端使用示波器测量眼图或抖动指标

上图为示波器连接方式

请注意由于不同的preset 会引起不同的摆幅有可能会超出目前设置scale 范围,

需要调试scale 来让波形有合适的大小,如下图

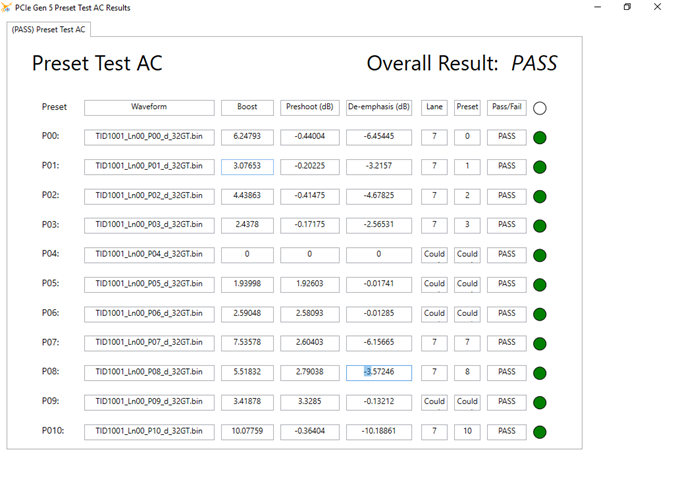

测试结果如下

4. 对每个预设值(PCIe Gen3 及以上为 0–9)重复上述测试(部分预设为厂商专有)。

5. 将测试结果与Compliance Mask进行比较验证。

标准与参考资料

PCI-SIG CEM 规范

PCI Express 基础规范(第 3.0 / 4.0 / 5.0 版本)

如需要更多测试详情和步骤,可以参考测试设备厂商的说明文档,以下是一个例子,其他厂商的测试方式类似。