--## 电子创新网图库均出自电子创新网,版权归属电子创新网,欢迎其他网站、自媒体使用,使用时请注明“图片来自电子创新网图库”,不过本图库图片仅限于网络文章使用,不得用于其他用途,否则我们保留追诉侵权的权利。 ##--

--电子创新网合作网站--

本网站转载的所有的文章、图片、音频视频文件等资料的版权归版权所有人所有,本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如果本网所选内容的文章作者及编辑认为其作品不宜公开自由传播,或不应无偿使用,请及时通过电子邮件或电话通知我们,以迅速采取适当措施,避免给双方造成不必要的经济损失。

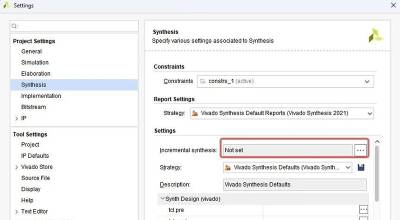

Vivado 是赛灵思(Xilinx)公司推出的一款综合性的设计工具套件,用于 FPGA(现场可编程门阵列)和 SoC(系统级芯片)的设计、开发和验证。它提供了一系列功能强大的工具,帮助工程师在各种应用领域中实现高性能、低功耗的硬件设计。

项目开发中常用的Vivado软件调试技巧(三)

在ILA核中,通常使用通过添加Marker线观察信号长度,如图1所示。如果删除Marker线,选中要删除的线然后右键,选择Delete Marker

把 Vivado 项目放心交给 Git:一篇 FPGA 工程师必读的实战指南

之前分享过一篇文章《FPGA 版本管理三种方式:你会选哪一种?》,评论区很多人都推荐使用Git进行版本管理,今天这篇文章主题就是使用Git进行备份指南。

项目开发中常用的Vivado软件调试技巧(一)

在项目中,利用JTAG采样低频数据时,受限于片上BRAM资源,采样的数据深度不能太深;另外,通常会受限于JTAG仿真器时钟也不能设置太低频率

分页

- 页面 1

- 下一页

Imagination中文技术社区精彩导读

EDA星球精彩导读

FPGA开发圈精彩导读

张国斌专栏

元件网精彩导读

- 1873774516_516738

- 2460440665_516737

- 1457585548_516736

- 780289498_516735

- 2283262460_516734

Recent comments