OP4800系列

FPGA处理器和I/O拓展箱

摆脱传统多FPGA解耦技术的束缚,在单块FPGA资源中支持更大规模的复杂电力电子电路模型(如功率换流器)。OPAL-RT前沿创新技术全面提升仿真能力:无与伦比的仿真精度、近乎零的延迟,能够实现迅捷开发和创新控制策略。专为双有源全桥(DAB)变换器与车载充电机(OBC)等应用量身打造,为您打开电力电子仿真技术的新未来。

VERSALTM FPGA

而不是UltraScale

☑ 逻辑单元更多,RAM容量更大;

☑ 58位容量DSP;

☑ 增强FPGA仿真频率(最高逻辑密度7nm平台);

☑ 4个ARM处理器(即将推出)。

卓越功能 实现性能全面提升

OP4810-IO和OP4815-IO扩展箱能够连接到OPAL-RT实时仿真器,配备计算能力卓越的AMD Versal™FPGA,可兼容当前最高版本的eHS(基于FPGA的电力电子仿真工具包),并提供更多更快的I/O。

全新版本eHS

OPAL-RT 基于FPGA的电力电子工具包 发布全新版本——eHS Gen5,在原有功能基础上增加了高级性能插件,是当前业界速度最快的基于FPGA的电力电子仿真工具包。

. 无需解耦

. FPGA核可扩展

. 皮秒级采样

. 可用于联合仿真

连通性

多达140个I/O 和12个5 Gbsp 高速SFP多模光纤模块连接器。

升级和扩展现有OPAL-RT系统

OP4810-IO和OP4815-IO扩展箱配备了最新的顶级Versal™ Prime计算引擎和更多更快的I/O,能够对现有的OPAL-RT系统(OP4610XG、OP5705XG和OP5707XG)进行升级和扩展。

OP48XX-IO 系列FPGA 处理器和 I/O 扩展箱可通过 PCIe 链接连接到现有的 OPAL-RT 实时仿真器;在实时仿真机中安装PCIe 主机适配器后,可通过光纤 SFP 链接实现 FPGA 相互之间的直接通信。

典型硬件在环(HIL)仿真应用

. LLC/CLLC 谐振变换器以及双有源全桥变换器的详细模型

. 大型功率转换应用

. 复杂电力电子系统(如大型UPS、越野车辆或列车电气传动系统)

. 基于FPGA的机械/电力电子/机电控制快速控制原型(控制带宽达 1+MHz)

. 用于 HVDC、FACTS 和 SST 应用的多电平转换器仿真

. 针对大规模 IBR 或EV集成的大量换流器和机器仿真

. 行波保护

. 大型配电网仿真

接口与连通性

① 电源和复位按钮(带LED指示灯)

② 光纤SFP端口 x 12(5Gbps)

③ 以太网RJ45端口 x 2(1 Gb/s)

④ 光纤同步接口

⑤ IRIG-B@1PPS 时钟同步接口(备用)

⑥ 用于JTAG编程的USB接口

⑦ FPGA 状态指示灯

⑧ LCD菜单按钮选择

⑨ LCD显示屏

⑩ 电源线插头和电源总开关

⑪ DB37 I/O 接口插槽 1

⑫ DB37 I/O 接口插槽 2

⑬ 接地螺丝

⑭ RS-422 DB9接口(6 Tx & 6 Rx)

⑮ PCI Express Gen2 x4 插槽

参数概览

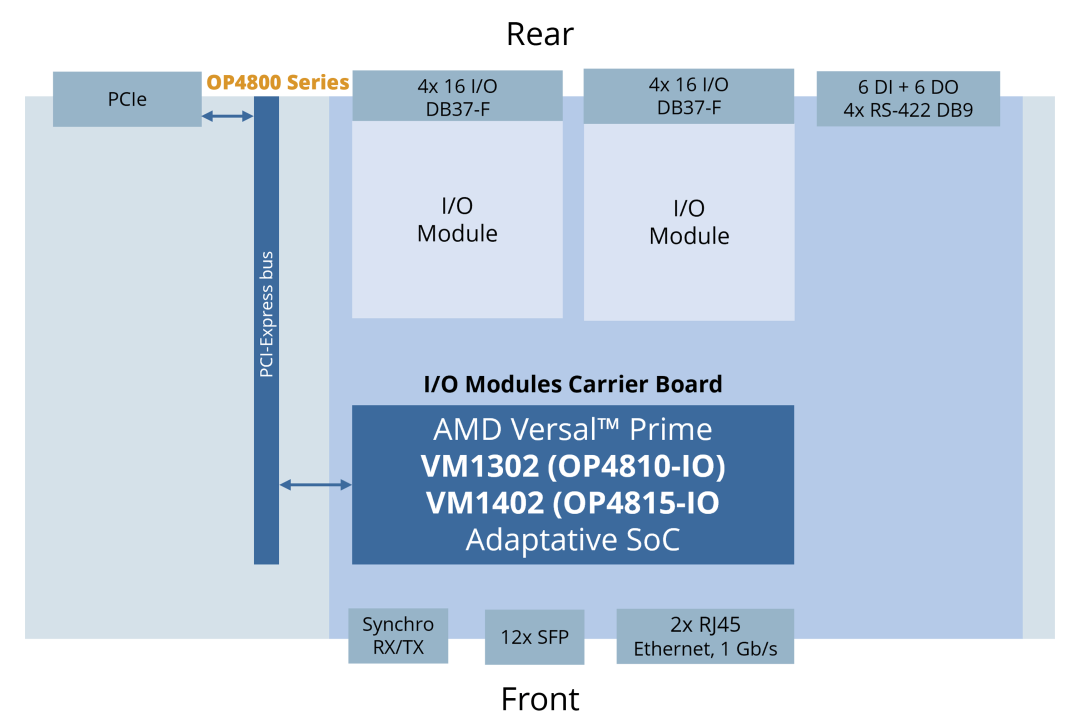

OP4810-IO / OP4815-IO 产品架构

OP48XX-IO扩展箱的核心是AMD VersalTM Prime自适应SoC和FPGA芯片。出厂安装2个I/O模块,每个模块包含4个DB37-F连接器,位于扩展箱后部,可提供多达64个I/O。

可通过PCIe链路实现下位机与OP48XX-IO FPGA之间的通信。OP48XX-IO还带有12个SFP插槽、2个以太网端口、TX/RX同步端口和4个DB9接口,用于RS422信号传输(6 Tx & 6 Rx)。

本文转载自:欧泊实时

ACAP

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

仿真与原型设计

FPGA(可编程门阵列)仿真与原型设计是在设计和验证数字电路时常用的方法。下面将简要介绍FPGA仿真和原型设计的基本概念:

FPGA仿真:

概念: FPGA仿真是通过软件工具模拟FPGA芯片上的电路行为,以验证设计的正确性。在仿真阶段,设计工程师可以评估电路的性能、时序、功耗等方面。

仿真工具: 常用的FPGA仿真工具包括ModelSim、VCS、XSIM等。这些工具允许设计工程师在计算机上运行仿真,观察信号波形,分析电路行为。

测试台构建: 在仿真中,通常需要构建测试台,即测试用例和输入数据,以验证设计在不同条件下的响应。

时序分析: 仿真工具可以提供时序分析,帮助设计工程师确保电路在不同工作条件下都满足时序要求。

FPGA原型设计:

概念: FPGA原型设计是将数字电路设计加载到FPGA芯片上,通过硬件验证电路的性能和功能。原型设计可以更准确地模拟实际硬件行为。

FPGA平台: 常用的FPGA平台包括Xilinx、Altera(现在是Intel FPGA)等。设计工程师将设计的RTL(寄存器传输级)代码综合到FPGA中。

验证: 在FPGA上验证设计的行为,包括逻辑功能、时序、接口等。通过实际硬件验证,可以检测到仿真中可能遗漏的问题。

调试: 在FPGA上进行调试,通过观察FPGA上的信号波形、使用硬件调试器等工具,解决设计中可能存在的问题。

FPGA仿真与原型设计的关系:

验证: 仿真是设计验证的一部分,而原型设计是验证的下一步,提供更接近实际硬件的环境。

调试: 仿真用于初步调试,但在原型设计中,设计工程师可以在真实硬件环境中调试问题。

性能评估: 仿真可以提供初步的性能估计,但原型设计更接近实际硬件,提供更准确的性能数据。

总体而言,FPGA仿真和原型设计是数字电路设计流程中不可或缺的两个环节,有助于确保设计的正确性、性能和可靠性。